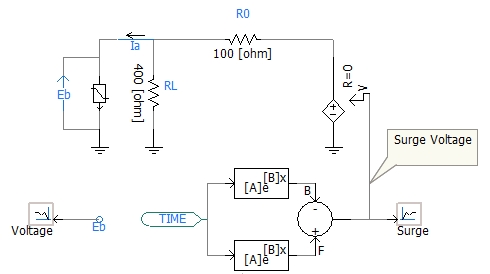

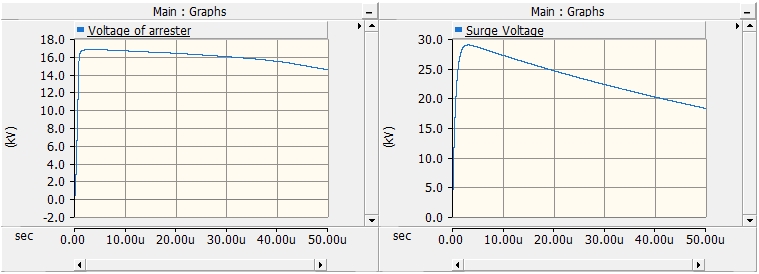

Hi, Sir or Madam. I computed a circuit network with the arrester using default I-V characteristics, as following Figure 1. The resistor RL is protected by the parralled arrester from a surge voltage. I suggest the resistance of arrester is extremely nonlinear with the voltage across it. For EMTDC, when voltage arise to the operating value at current step, the resistance of arrester will fall sharply that make the RL nearly short-circuit at next step. And the resistor R0 will be mainly subjected to the surge voltage, the arrester, in turn, will switch again at following step. During over-voltage simulation, I think it brings about the violent swing of arrester between the On- and Off- state. However,the simulation result of arrester is completely different from what I described above,as shown in Figure 2. My question is how the software solve the circuit networks with a arrester?

Figure 1:

Figure 2 :

Add New Comment